Design Tradeoffs

本章从CMOS的电能消耗出发,讲如何减少不必要的能量损失,同时也讲了很多时间和空间的tradeoff.

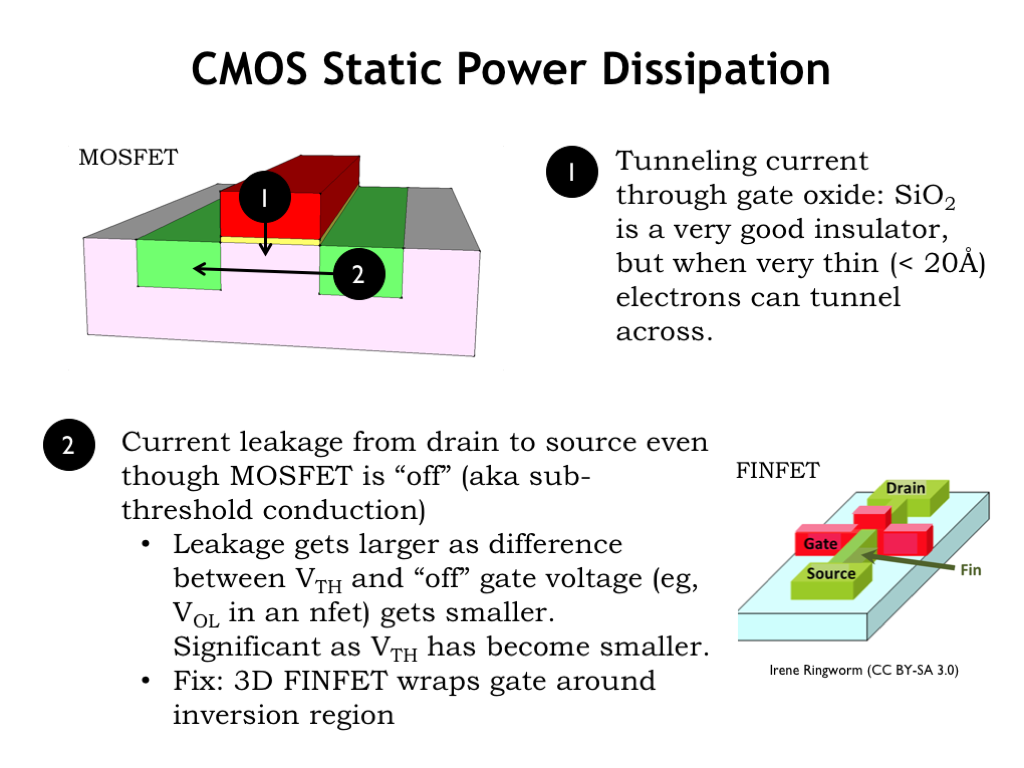

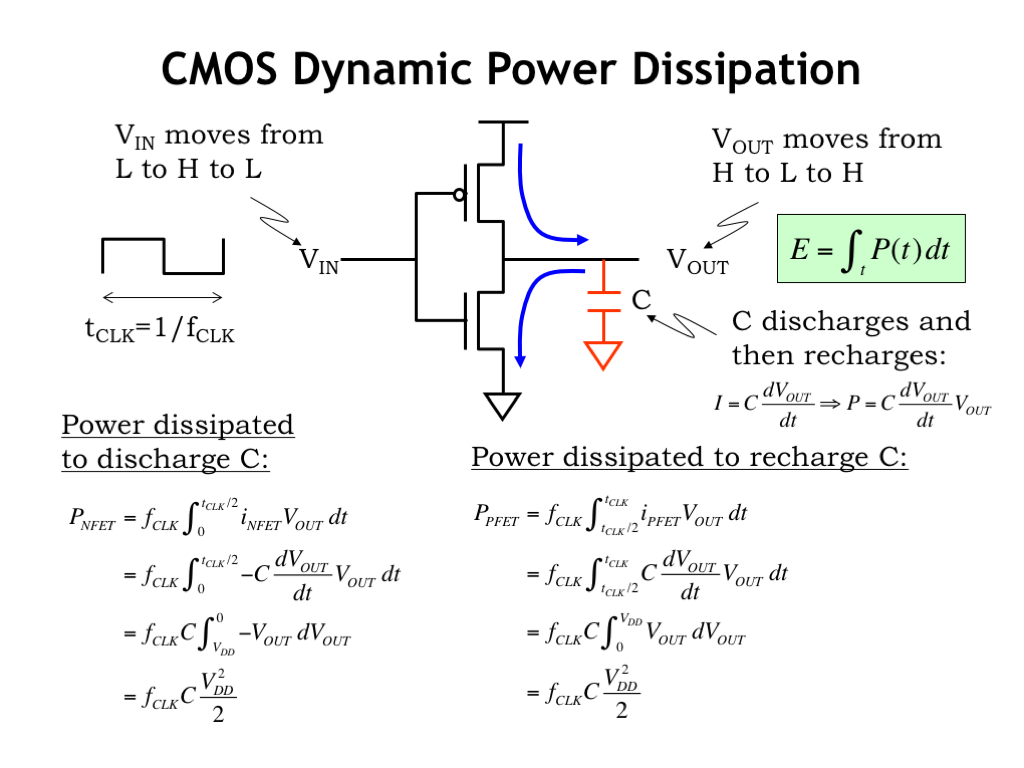

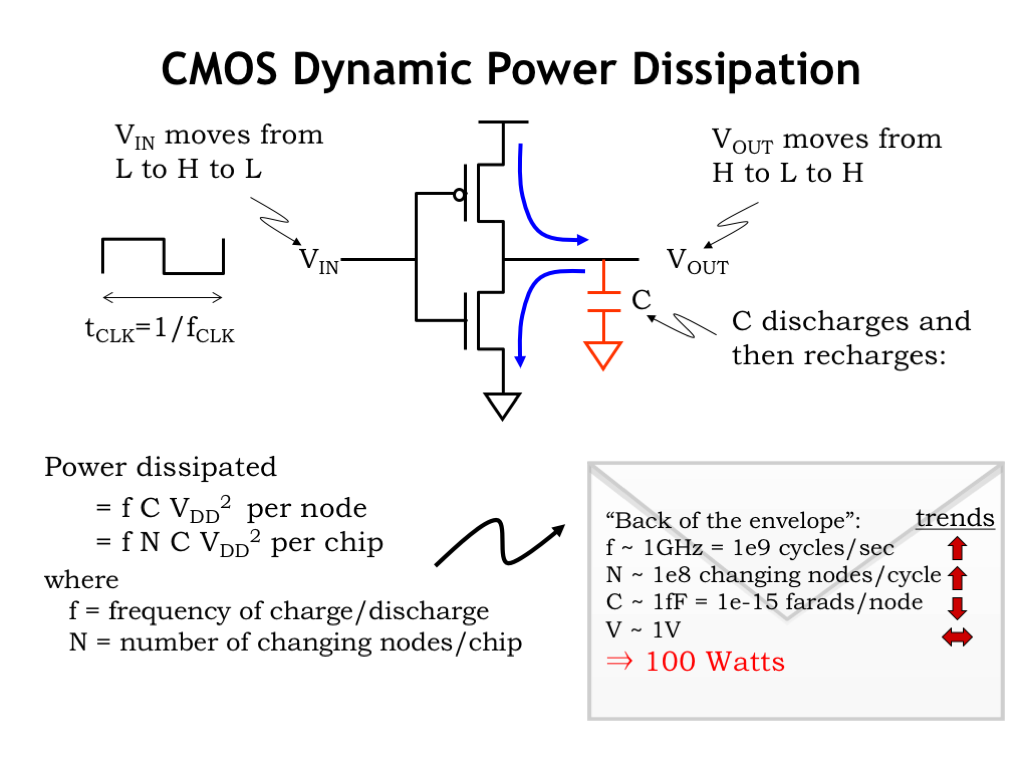

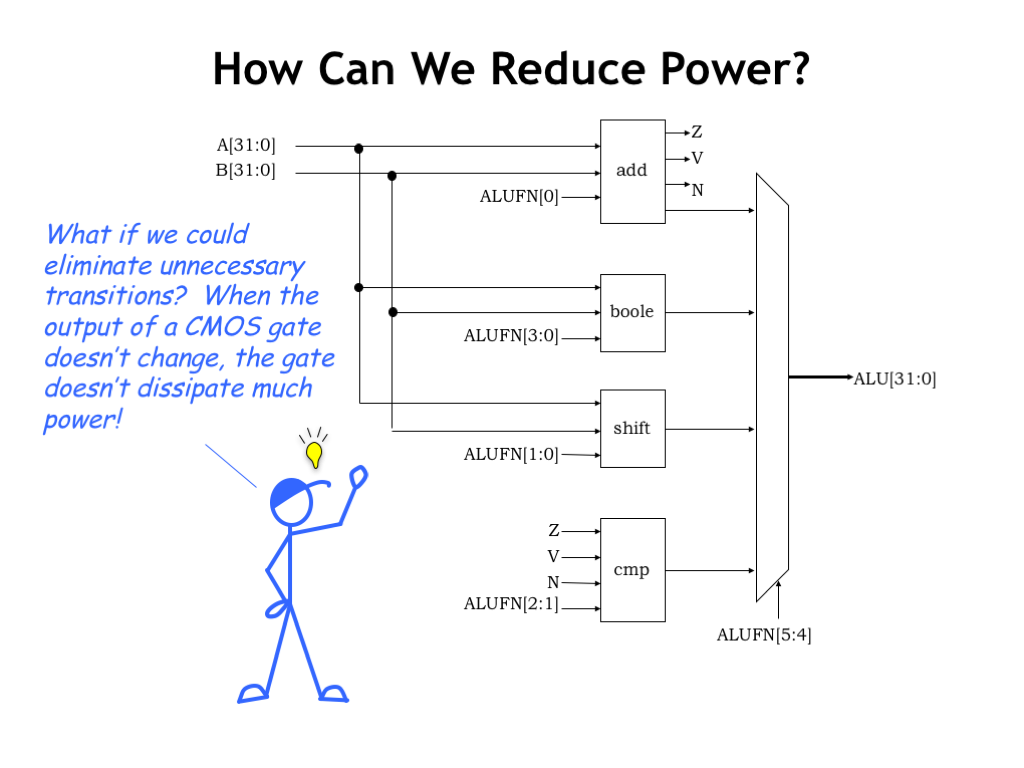

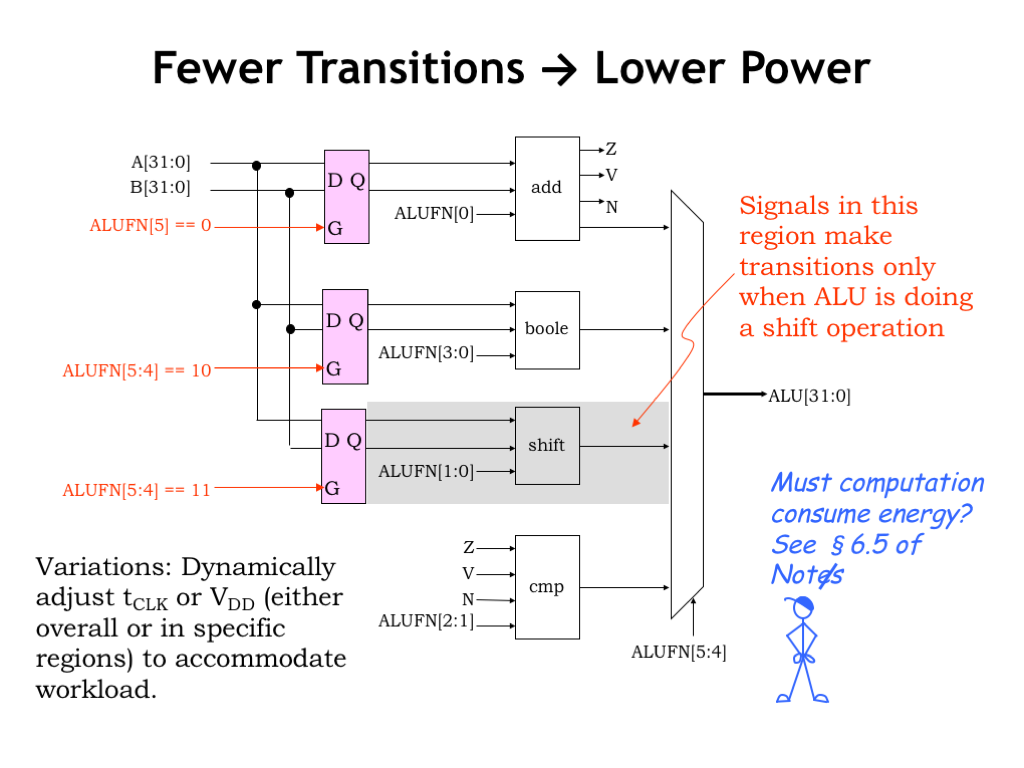

Power dissipation

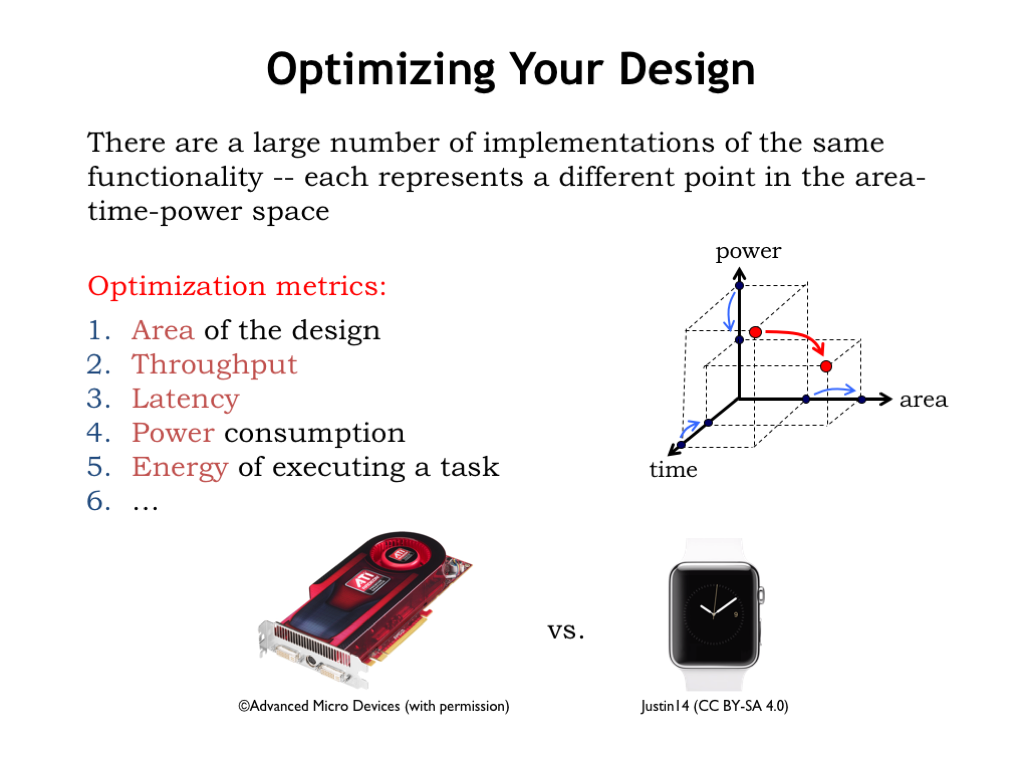

电路优化的几个metrics

CMOS能耗

一个减小能耗的简单例子

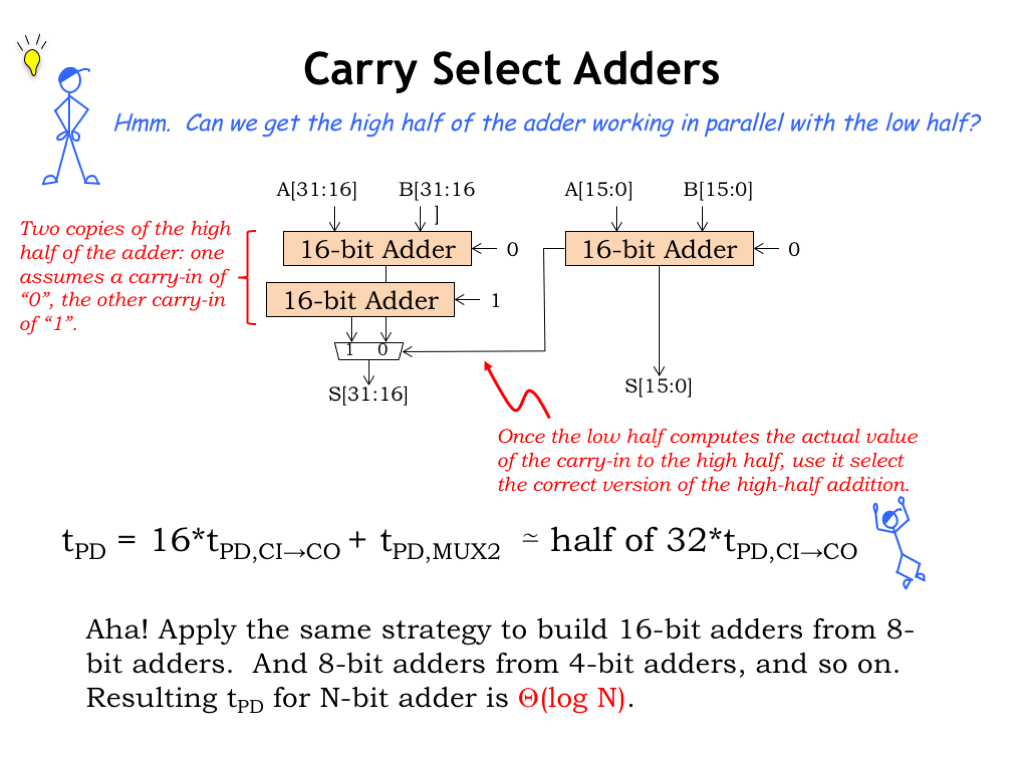

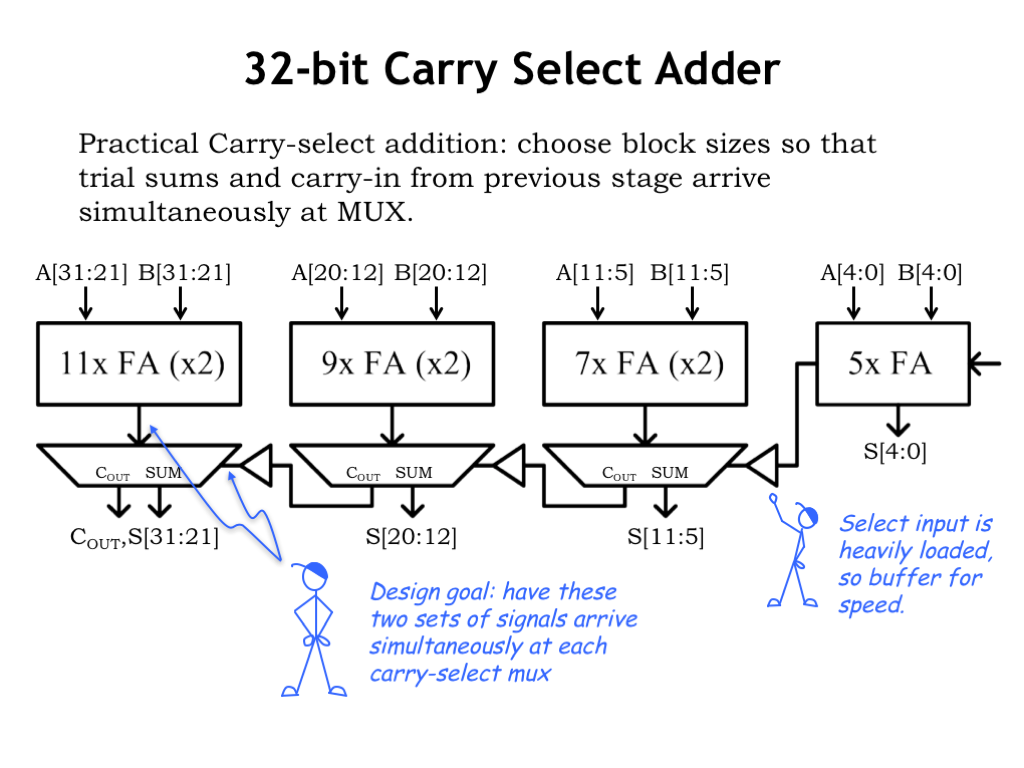

Carry-select Adder

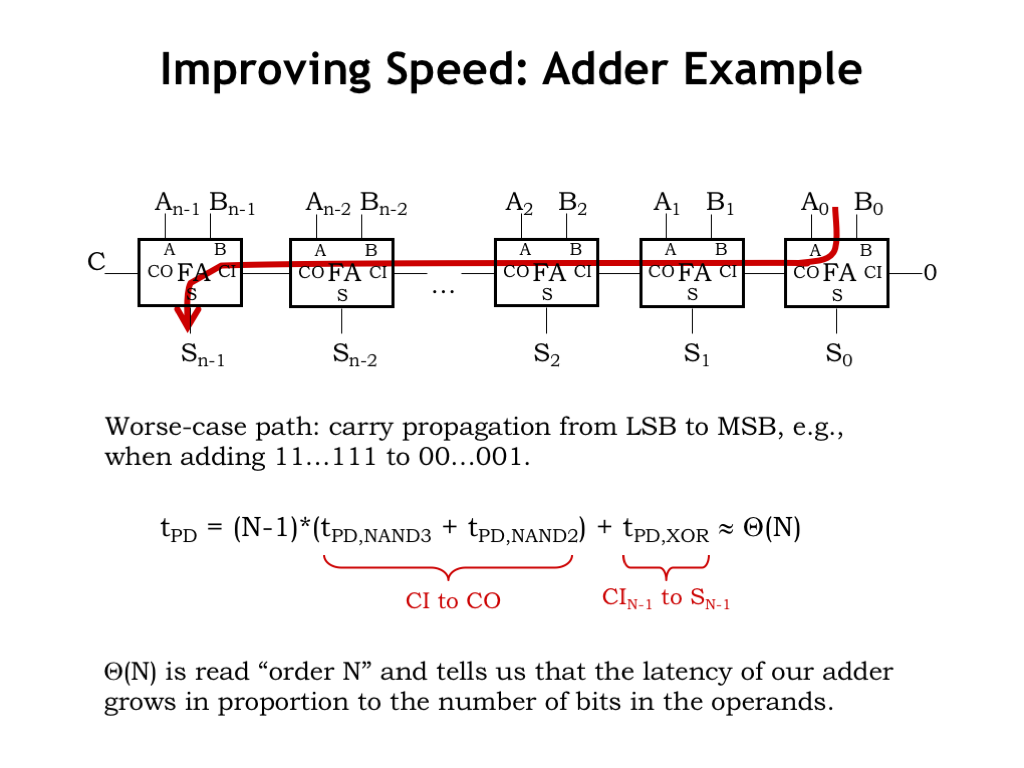

设计一个N位的加法器,最直观的设计就是把N个全加器串联。

但是这样的$t_{PD}$是$\theta(N)$级别的。

现在将一个32位的加法器分成两个16位的部分分别计算再组合,$t_{PD}$就差不多减小了一半。

按这个思路一直二分下去,$t_{PD}$便能达到$O(\log n)$。

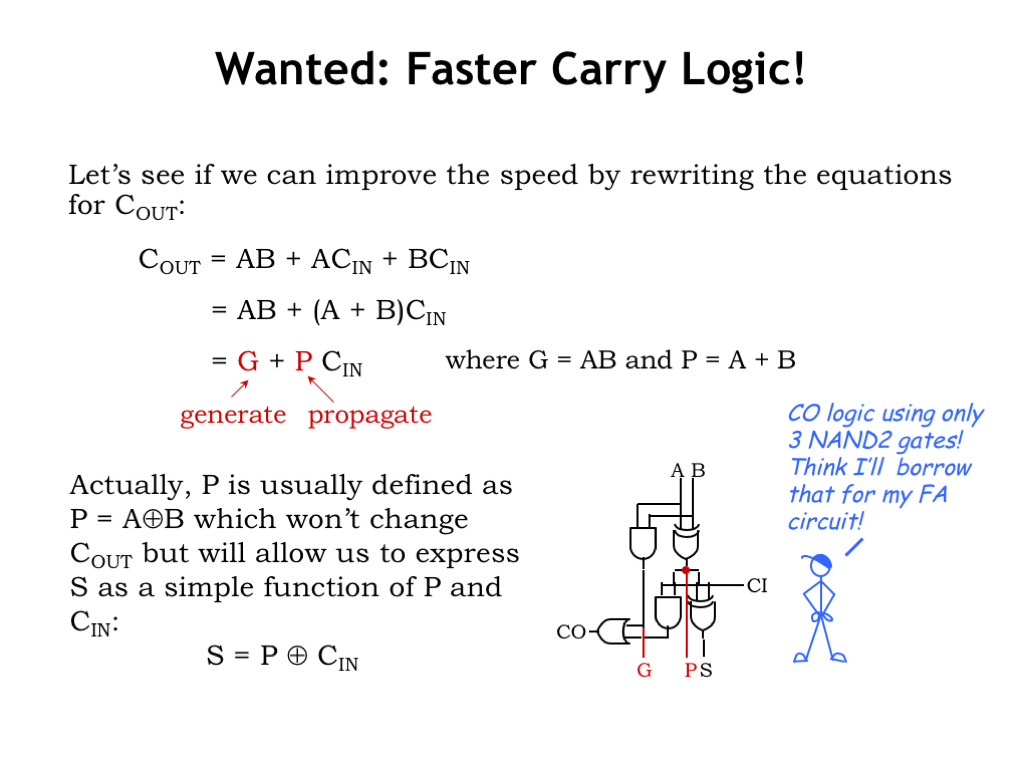

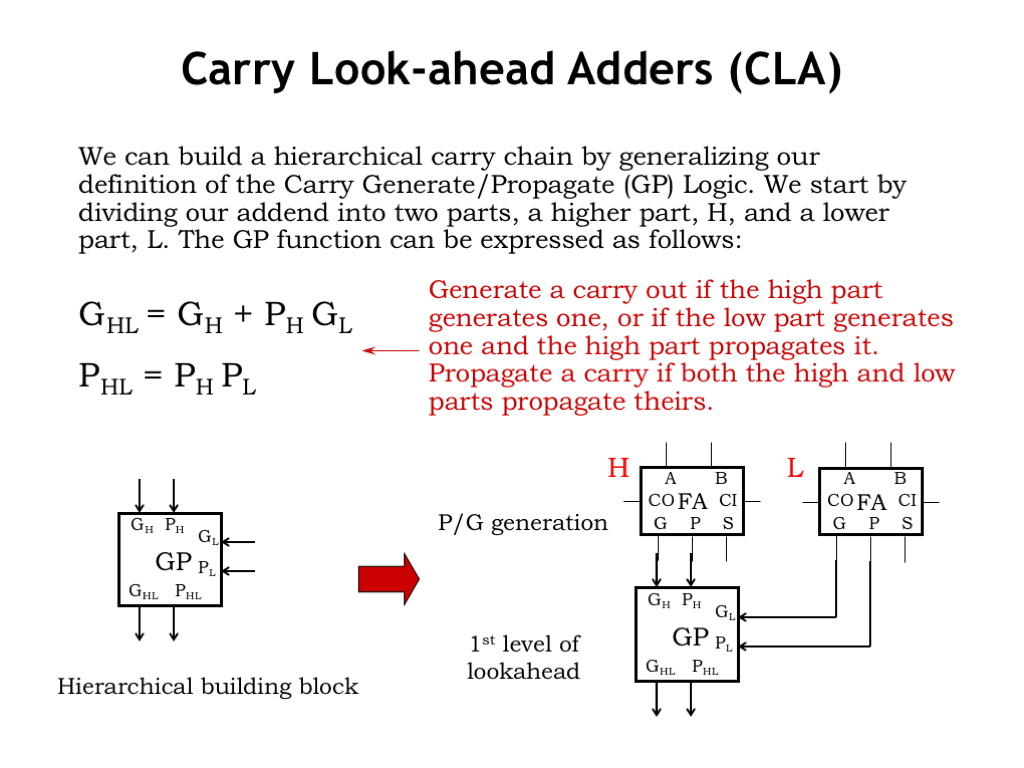

Carry lookahead Adder(CLA)

从$C_{out}$的计算公式中可以看出,一个FA的输入可以转换成3个变量$P$,$G$和$C_{in}$ ,其中只有$C_{in}$需要该位的前一位的$C_{out}$。

如果知道了两个相邻位置的$P$和$G$,那么可以把这两位当作一个整体,计算出这个整体的$P$和$G$,这时$P$和$G$任然还保留着原来的性质,所以,我们可以用倍增来计算整个电路的$P$和$G$。

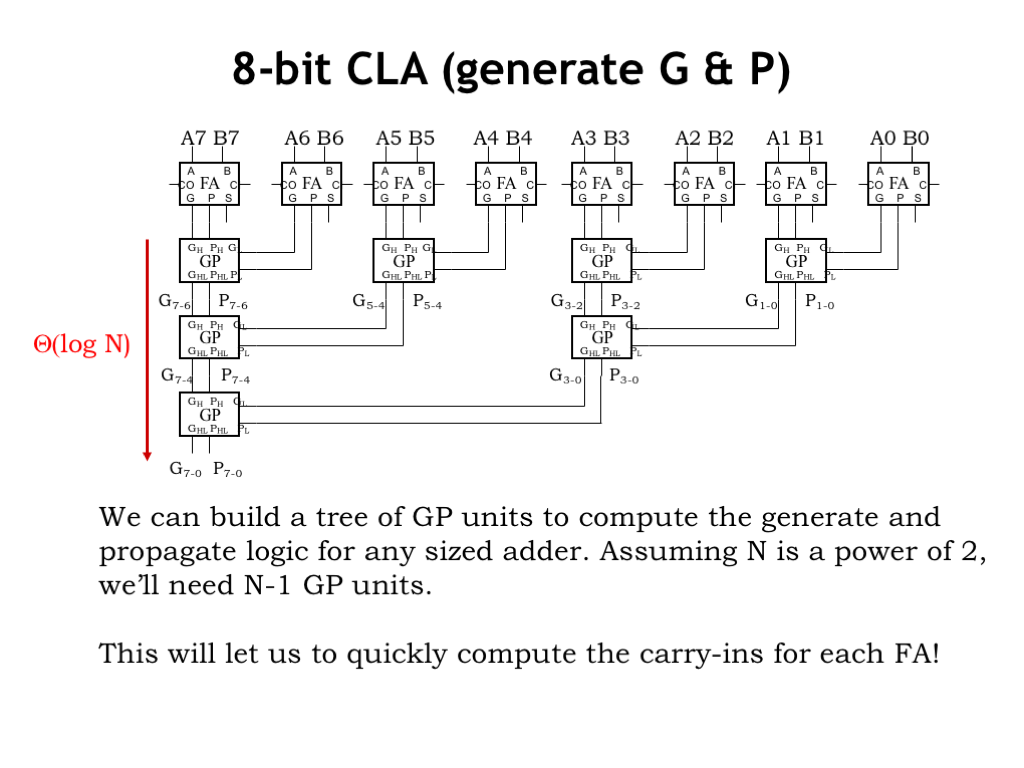

下图是一个8-bits的CLA的G&P generate的部分:

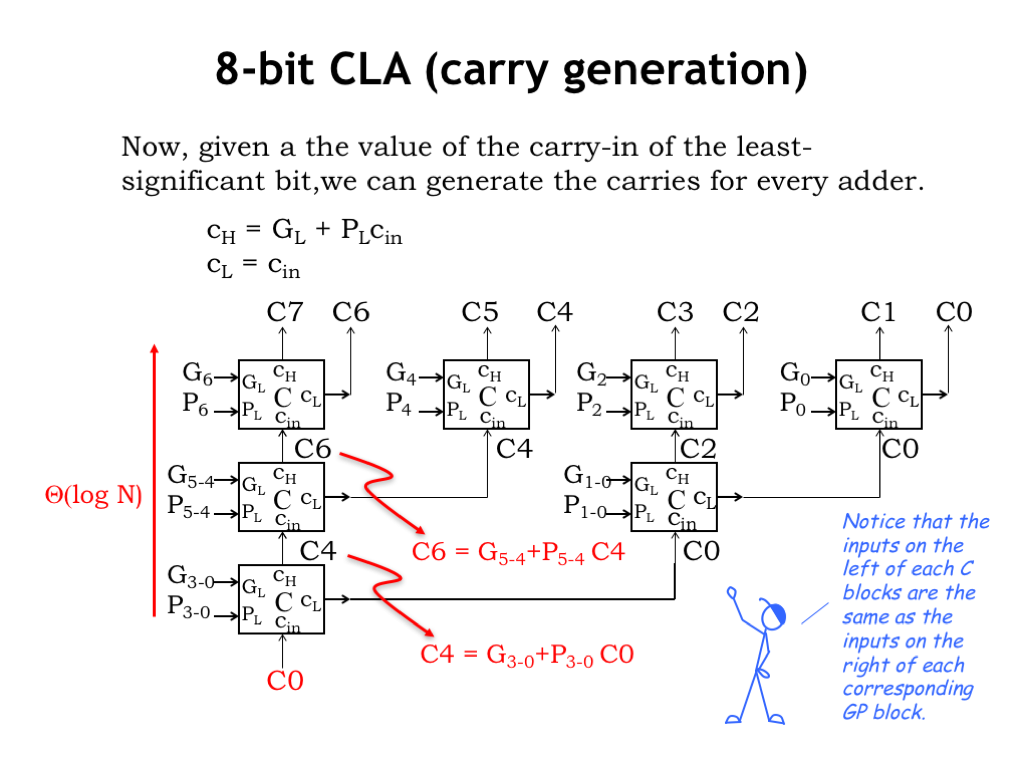

然后是计算Carry的方法:

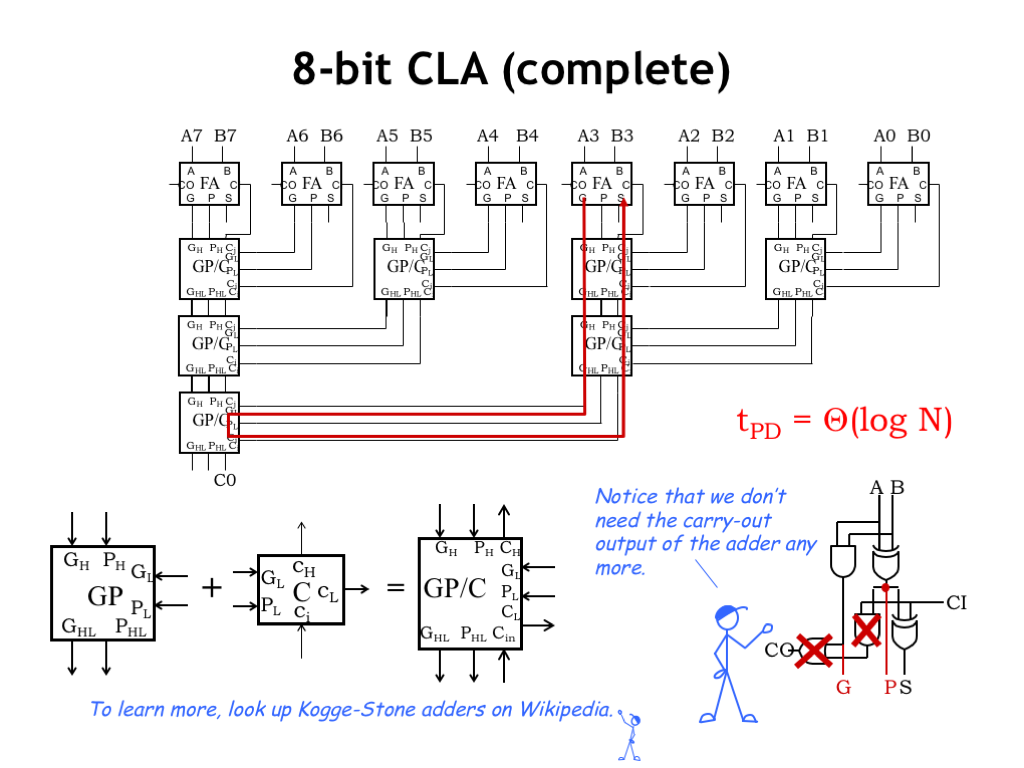

完整版:

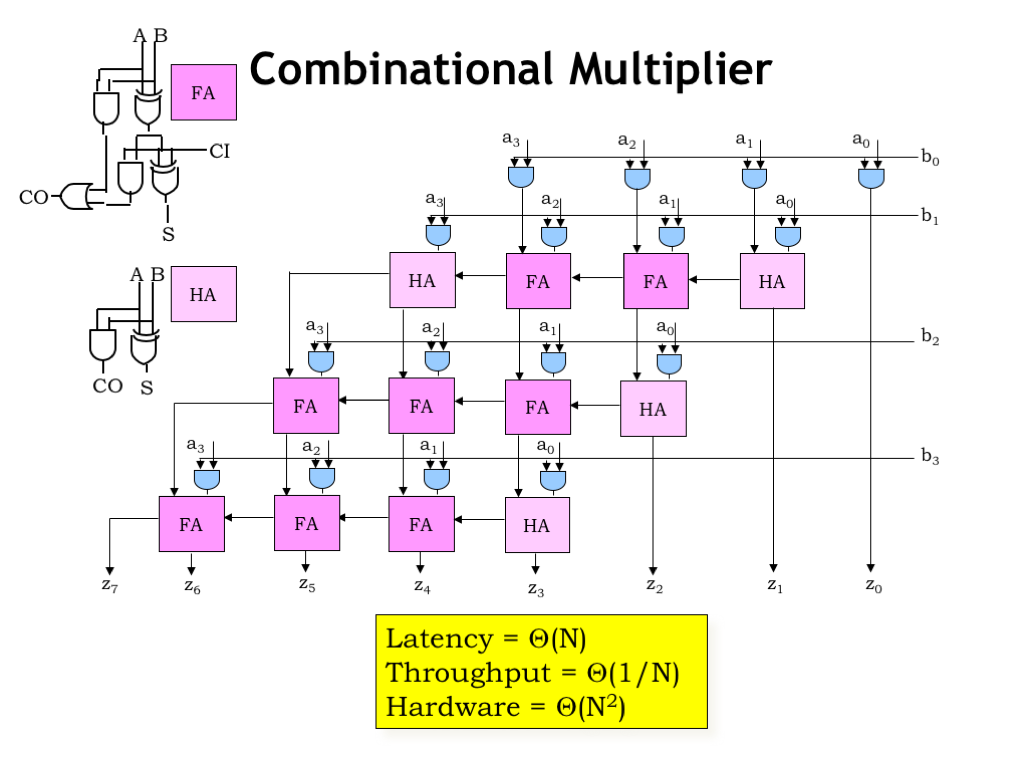

Multiplier

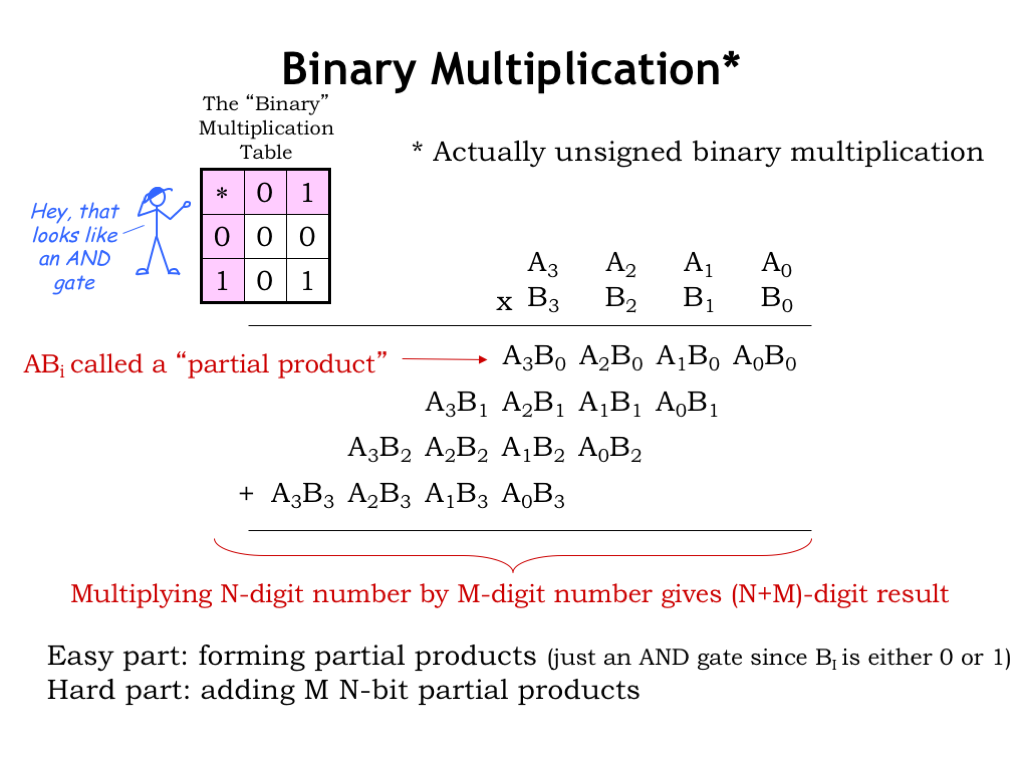

binary multiplication

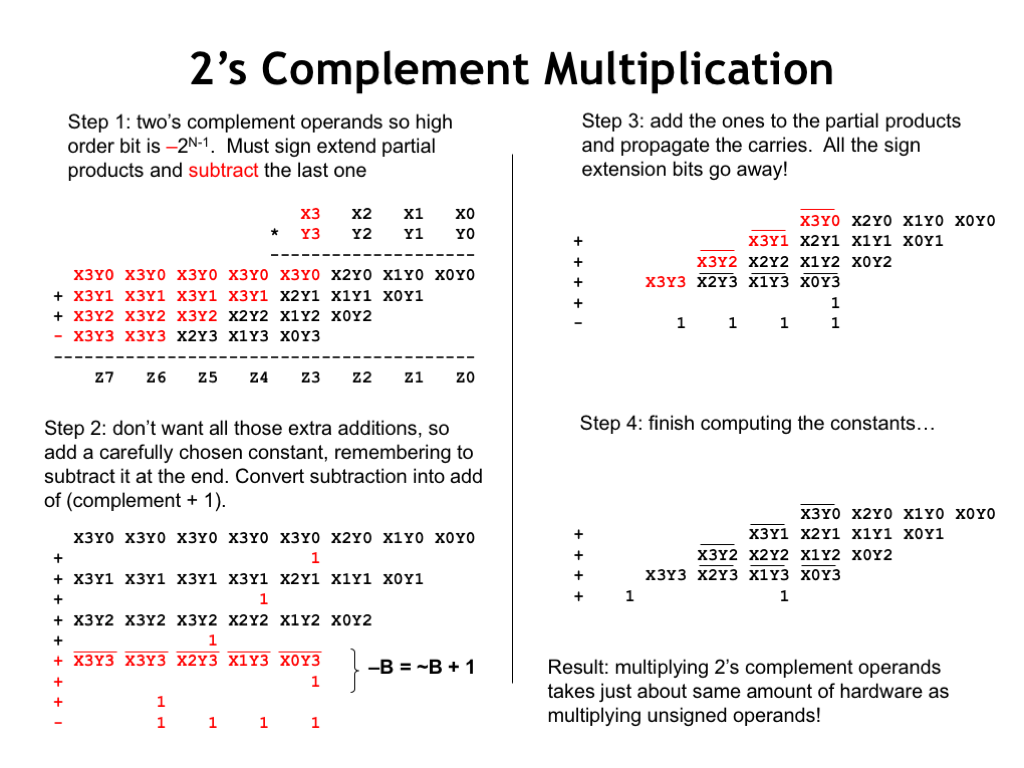

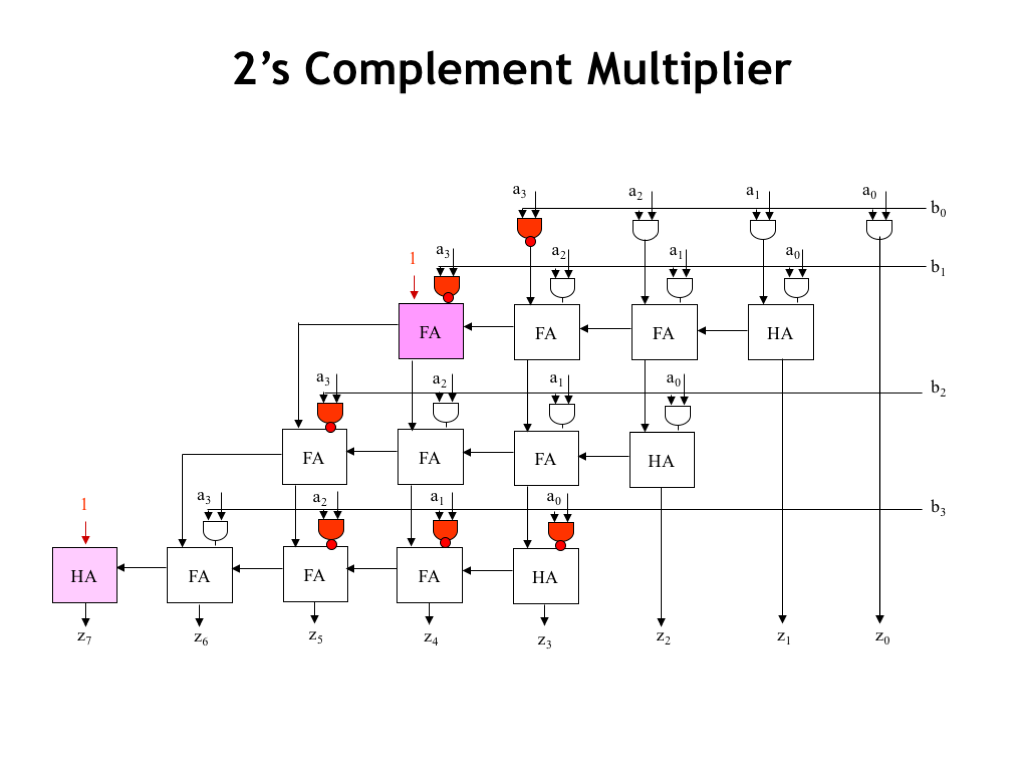

就是普通的竖式乘法,但是要注意如果值是补码,那最高位的全值为$-2^{N-1}$而不是$2^{N-1}$。

如下是值为补码的情况:

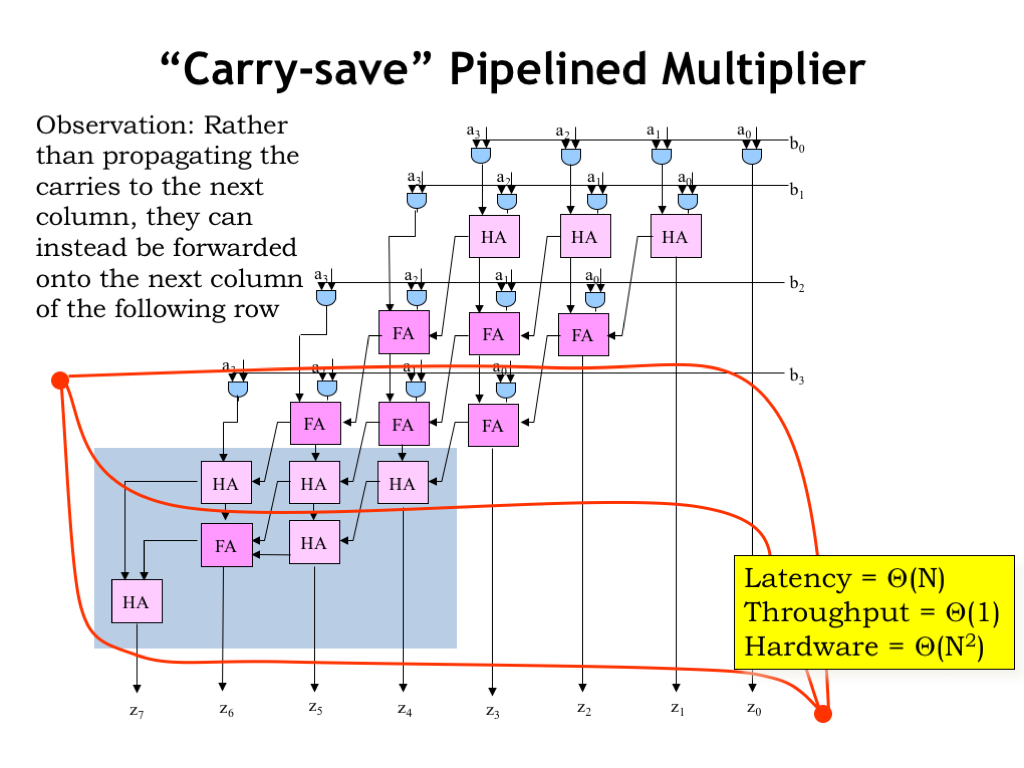

pipelined multiplier

虽然pipeline化了,但每个stage的$t_{PD}$还是$O(N)$的,主要问题在于要按行传递carry。

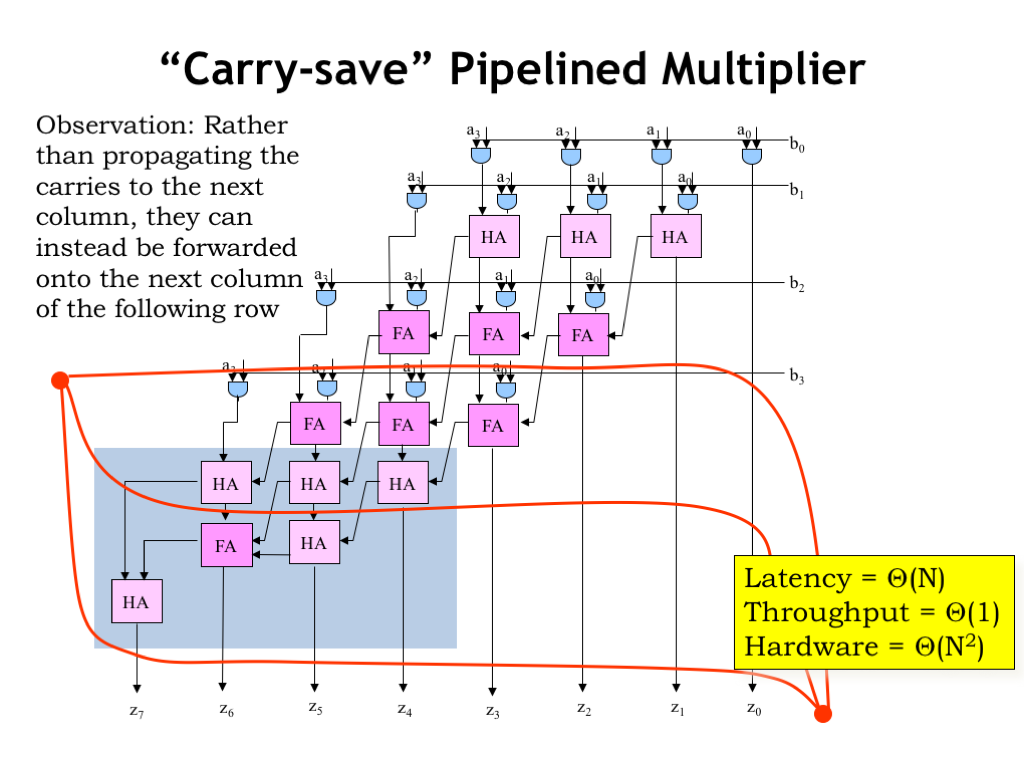

Carry-save multiplier

讲每行需要传递的carry降到下一行(反正都是加在同一列,所以对结果没影响),这样可以将每个stage的$t_{PD}$优化到$O(1)$,但是需要更多的行,也就是面积增加了。

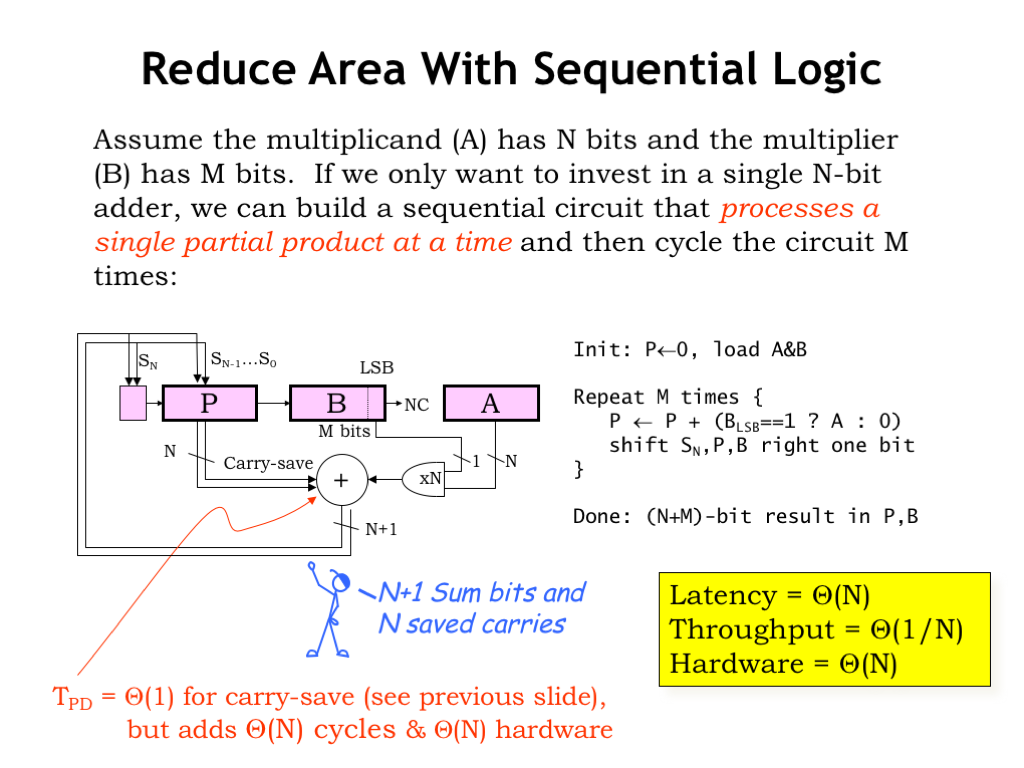

用时序电路减少面积

求和->移位->求和。

Summary